# AN-1428 LM3370 Evaluation Board

#### 1 Introduction

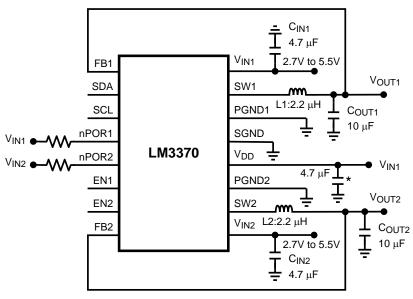

The LM3370 evaluation board is a working demonstration of a DUAL step down DC-DC converter. This application note contains information about the evaluation board. For more details and electrical characteristic on the dual buck converter operation, see the *LM3370 Dual Synchronous Step-Down DC-DC Converter with Dynamic Voltage Scaling Function Data Sheet* (SNVS406).

#### 2 General Description

The LM3370 is a dual step-down DC-DC converter optimized for powering ultra-low voltage circuits from a single Li-Ion cell or 3 cell NiMH/NiCd batteries. Automatic intelligent switching between PWM low-noise and PFM low current mode offers improved system efficiency. The I<sup>2</sup>C compatible offers dynamic controls of the output voltages, Auto PFM/PWM mode selection and other enabling enchantment features such as power-on-reset (nPOR) and spread spectrum.

## 3 Operating Conditions

- V<sub>IN</sub> range: 2.7V ≤ V<sub>IN</sub> ≤ 5.5V

- Recommended load current: 0 to 600mA I<sup>2</sup>C Compatible Interface

- V<sub>OUT1</sub> (1V to 2V at 50mV step increment)

- V<sub>OUT2</sub> (1.8V to 3.3V at 100mV steps increment).

Package

- TLA20CWA micro SMD, (3.0mm x 2.0mm x 0.6mm)

- LLP16 non-pullback, (4mm x 5mm x 0.8mm)

All trademarks are the property of their respective owners.

Typical Application

www.ti.com

### 4 Typical Application

\* Optional Capacitor

#### **Figure 1. Typical Application Circuit**

## 5 Operating Information

The LM3370SD evaluation board is pre-programmed to 1.2V at  $V_{OUT1}$  and 3.3V at  $V_{OUT2}$  for evaluation purpose (no additional interface hardware is needed). If different default output option is desired, the same evaluation board can be used to demount the existing device and replace with a new voltage option (voltage option can be ordered from TI's website at www.ti.com).

The device comes with the following default setting: Auto PFM and PWM transition mode when the  $I^2C$  compatible interface is not enabled. For other settings,  $I^2C$  compatible interface must be used to enable all other functions. Registers information are listed on page 4 for  $I^2C$  compatible interface.

### 6 Powering Up the Evaluation Board

- Apply a voltage at the "Vin\_EXT" pin only (not Vin\_IO).

- All logic pins are tied to "Vin" on the evaluation board

- Do not power the "Vin\_IO" pin unless powering the logic pins via an external source. (Jumper at Vin\_IO must be removed.)

- $V_{DD}$  pin is tied to  $V_{IN1}$  &  $V_{IN2}$  on the evaluation board, no additional connection required. (For any reason if  $V_{DD}$  is not directly tied to  $V_{IN}$ ,  $V_{DD}$  needs to be equal or greater than the two inputs ( $V_{IN1}$  or  $V_{IN2}$ ) for proper operation.)

## 7 I<sup>2</sup>C Interface Ready

If interface capability is available via I<sup>2</sup>C compatible, the SDA & SCL test pins of the evaluation board are brought out for such function. The SDA & SCL pins of the evaluation board are connected to 2 k $\Omega$  resistors and pulled up to V<sub>IN</sub> pin.

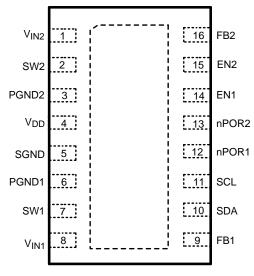

## 8 Package Marking Information

Figure 2. Top View

## 9 Pin Descriptions (WSON)

| 1  | V <sub>IN2</sub> | Power supply voltage input to PFET and NFET switches for Buck2                                                                             |  |

|----|------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|

| 2  | SW2              | Buck 2 Switch pin                                                                                                                          |  |

| 3  | PGND2            | Buck 2 Power Ground                                                                                                                        |  |

| 4  | V <sub>DD</sub>  | Signal supply voltage input, $V_{DD}$ must be equal or greater of the two inputs ( $V_{IN1}$ or $V_{IN2}$ )                                |  |

| 5  | SGND             | Signal GND                                                                                                                                 |  |

| 6  | PGND1            | Buck 1 Power Ground                                                                                                                        |  |

| 7  | SW1              | Buck 1 Switch pin                                                                                                                          |  |

| 8  | V <sub>IN1</sub> | Power supply voltage input to PFET and NFET switches fo Buck1                                                                              |  |

| 9  | FB1              | Analog feedback input for Buck 1                                                                                                           |  |

| 10 | SDA              | $I^2C$ Compatible Data, a 2 k $\Omega$ pull up resistor is required                                                                        |  |

| 11 | SCL              | $I^2C$ Compatible Data, a 2 k $\Omega$ pull up resistor is required                                                                        |  |

| 12 | nPOR1            | Power ON Reset for Buck 1, Open drain output low when Buck 2 output is 92% of target output. A 100 k $\Omega$ pull up resistor is required |  |

| 13 | nPOR2            | Power ON Reset for Buck 2, Open drain output low when Buck 2 output is 92% of target output. A 100 k $\Omega$ pull up resistor is required |  |

| 14 | EN1              | Buck 1 Enable                                                                                                                              |  |

| 15 | EN2              | Buck 2 Enable                                                                                                                              |  |

| 16 | FB2              | Analog feedback input for Buck 2                                                                                                           |  |

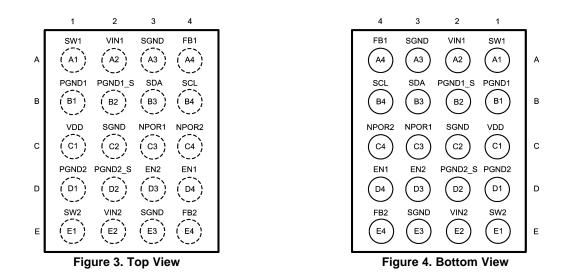

Package Marking Information (DSBGA)

## **10** Package Marking Information (DSBGA)

## 11 Pin Descriptions (DSBGA)

## Table 2. Pin Descriptions (DSBGA)

| Pin No | Name             | Description                                                                                                                                |  |

|--------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|

| A1     | SW1              | Buck 1 Switch Pin                                                                                                                          |  |

| A2     | V <sub>IN1</sub> | Power supply voltage input to PFET and NFET switches for Buck 1                                                                            |  |

| A3     | SGND             | Signal GND                                                                                                                                 |  |

| A4     | FB1              | Analog Feedback Input for Buck 1                                                                                                           |  |

| B1     | PGND1            | Buck 1 Power Ground                                                                                                                        |  |

| B2     | PGND1_S          | Buck 1 Power Ground Sense                                                                                                                  |  |

| B3     | SDA              | $I^2C$ Compatible Data, a 2 kΩ pull up resistor is required                                                                                |  |

| B4     | SCL              | $I^2C$ Compatible Clock, a 2 k $\Omega$ pull up resistor is required                                                                       |  |

| C1     | V <sub>DD</sub>  | Signal supply voltage input, $V_{DD}$ must be equal or greater of the two inputs ( $V_{IN1} \& V_{IN2}$ )                                  |  |

| C2     | SGND             | Signal GND                                                                                                                                 |  |

| C3     | nPOR1            | Power ON Reset for Buck 1, Open drain output Low when Buck 1 output is 92% of target output. A 100 k $\Omega$ pull up resistor is required |  |

| C4     | nPOR2            | Power ON Reset for Buck 2, Open drain output Low when Buck 2 output is 92% of target output. A 100 k $\Omega$ pull up resistor is required |  |

| D1     | PGND2            | Buck 2 Power Ground                                                                                                                        |  |

| D2     | PGND2_S          | Buck 2 Power Ground Sense                                                                                                                  |  |

| D3     | EN2              | Buck 2 Enable                                                                                                                              |  |

| D4     | EN1              | Buck 1 Enable                                                                                                                              |  |

| E1     | SW2              | Buck 2 Switch Pin                                                                                                                          |  |

| E2     | V <sub>IN2</sub> | Power supply voltage input to PFET and NFET switches for Buck 2                                                                            |  |

| E3     | SGND             | Signal GND                                                                                                                                 |  |

| E4     | FB2              | Analog feedback for Buck 2                                                                                                                 |  |

| Buck Output Voltage Selection Codes |            |                            |  |  |

|-------------------------------------|------------|----------------------------|--|--|

| Data Code                           | Buck_1 (V) | Buck_2 (V)                 |  |  |

| 00000                               | NA         | NA                         |  |  |

| 00001                               | NA         | 1.8                        |  |  |

| 00010                               | NA         | 1.85 or 1.9 <sup>(1)</sup> |  |  |

| 00011                               | NA         | 2.0                        |  |  |

| 00100                               | NA         | 2.1                        |  |  |

| 00101                               | 1.00       | 2.2                        |  |  |

| 00110                               | 1.05       | 2.3                        |  |  |

| 00111                               | 1.10       | 2.4                        |  |  |

| 01000                               | 1.15       | 2.5                        |  |  |

| 01001                               | 1.20       | 2.6                        |  |  |

| 01010                               | 1.25       | 2.7                        |  |  |

| 01011                               | 1.30       | 2.8                        |  |  |

| 01100                               | 1.35       | 2.9                        |  |  |

| 01101                               | 1.40       | 3.0                        |  |  |

| 01110                               | 1.45       | 3.1                        |  |  |

| 01111                               | 1.50       | 3.2                        |  |  |

| 10000                               | 1.55       | 3.3                        |  |  |

| 10001                               | 1.60       | NA                         |  |  |

| 10010                               | 1.65       | NA                         |  |  |

| 10011                               | 1.70       | NA                         |  |  |

| 10100                               | 1.75       | NA                         |  |  |

| 10101                               | 1.80       | NA                         |  |  |

| 10110                               | 1.85       | NA                         |  |  |

| 10111                               | 1.90       | NA                         |  |  |

| 11000                               | 1.95       | NA                         |  |  |

| 11001                               | 2.00       | NA                         |  |  |

Table 3. Output Selection Table via I<sup>2</sup>C Programing

<sup>(1)</sup> Can be trimmed at the factory at 1.85V or 1.9V using the same trim code.

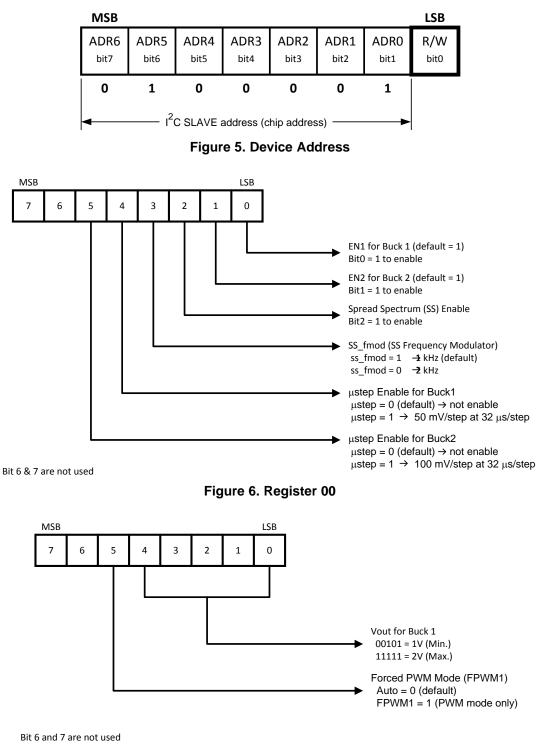

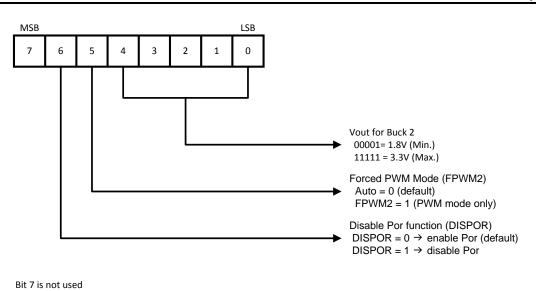

#### 12 Registers Information

Figure 7. Register 01

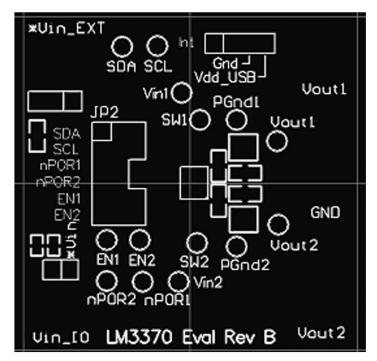

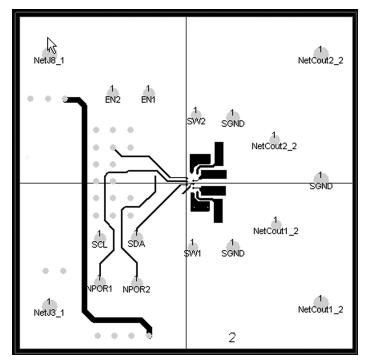

## 13 Evaluation Board Layout (WSON)

LM3370SD is a 4-layer board designed to maximize the performance fo the device.

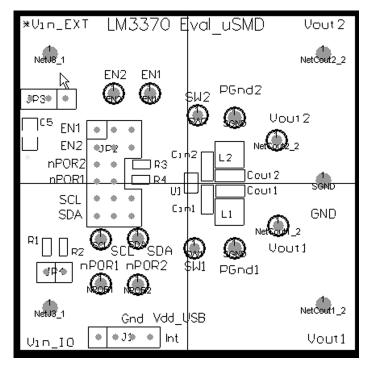

Figure 9. Silk Screen

Evaluation Board Layout (WSON)

www.ti.com

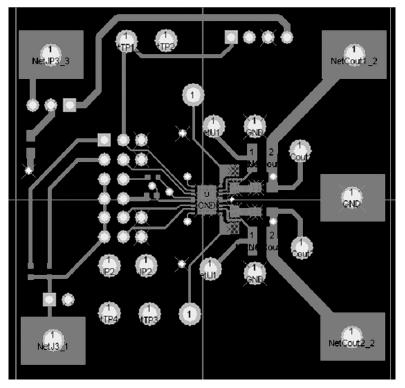

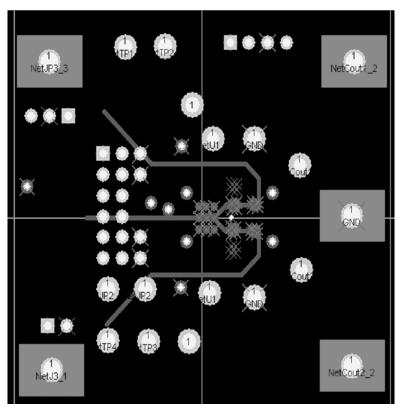

Figure 10. Top Layer

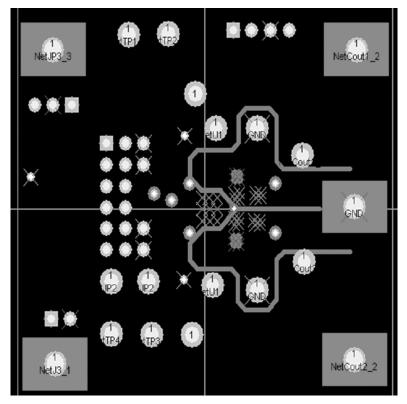

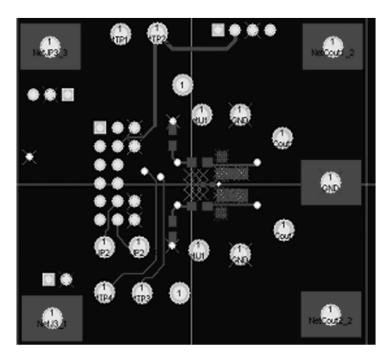

Figure 11. Mid Layer 1

Figure 12. Mid Layer 2

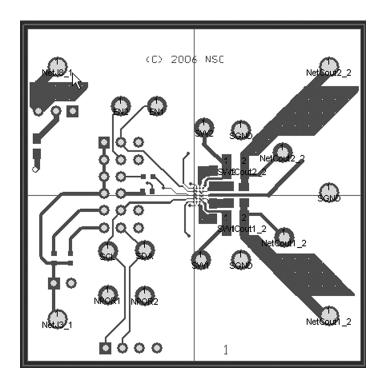

Figure 13. Bottom Layer

Evaluation Board Layout (DSBGA)

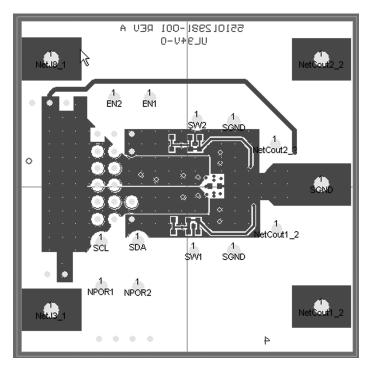

## 14 Evaluation Board Layout (DSBGA)

The LM3370TL applications is of similar layout to the LLP board with the exception of the SCL, SDA pins. When using the USB interface cable the order of these pins is reversed.

Figure 14. Silk Screen

Figure 15. Top Layer

Figure 16. Mid Layer 1

Figure 17. Bottom Layer

## 15 Bill of Materials (BOM)

| Component Name                                                                 | Manufacture | Manufacture No           |                                   | Specification      |

|--------------------------------------------------------------------------------|-------------|--------------------------|-----------------------------------|--------------------|

| LM3370                                                                         |             | <u>i</u>                 |                                   | -                  |

| C <sub>IN1</sub> and C <sub>IN2</sub>                                          | TDK         | C2012X5R0J475K           | C2012X5R0J475K                    |                    |

|                                                                                | muRata      | GRM219R60J475KE19D       | GRM219R60J475KE19D                |                    |

| $C_{OUT1}$ and $C_{OUT2}$                                                      | TDK         | C2012X5R0J106K           | C2012X5R0J106K                    |                    |

|                                                                                | muRata      | GRM219R60J106KE19D       | GRM219R60J106KE19D                |                    |

| L1 & L2                                                                        | Taiyo-Yuden | NR3015T-2R2M             | NR3015T-2R2M                      |                    |

| R1-2(SDA+SCL)                                                                  | Vishay      |                          |                                   |                    |

| R3-4 (nPOR1-2)                                                                 | Vishay      |                          |                                   |                    |

| <b>TEST Pins and Con</b>                                                       | inectors    |                          |                                   |                    |

| V <sub>OUT1</sub> ,V <sub>OUT2</sub> , GND, *Vin_EXT, Vin_IO                   |             |                          |                                   |                    |

| nPOR1. nPOR2, SDA, SCL, PGND1,<br>PGND2, V <sub>IN1</sub> , V <sub>IN2</sub> , |             |                          |                                   |                    |

| Jumper                                                                         |             |                          |                                   |                    |

| SDA/SCL/nPOR1                                                                  |             | Jumpers Female(Handle ce | Jumpers Female(Handle centerline) |                    |

| nPOR2/EN1/EN2                                                                  |             |                          |                                   |                    |

| *VIN & *VIN_IO                                                                 |             | _                        |                                   |                    |

| *VIN_IO                                                                        |             |                          |                                   | 2 in series (2x1)  |

| *VIN_EXT                                                                       |             |                          |                                   | 2 in series (2x1)  |

| Int                                                                            |             | Berk stick               | Header                            | 4 in series (4x1)  |

| JP2:SDA & SCL                                                                  |             |                          |                                   | 6 in series(6x2)   |

| nPOR1/ nPOR2/EN1& EN2                                                          |             |                          |                                   | 2 in series 2(2x1) |

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                          | Applications                  |                                   |

|------------------------------|--------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio         | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com         | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com     | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com              | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com               | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks        | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com         | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com             | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com             | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com   | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com          |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap          | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconne | ectivity                      |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2013, Texas Instruments Incorporated